## **Description**

The RoHS 6/6 compliant STC5420 is a single chip clock synchronization solution for applications in SDH/SETS, SONET, and Synchronous Ethernet network elements. The device is fully compliant with ITU-T G.813 option 1 and 2, G.8262 EEC Opt1 and Opt2 and Telcordia GR1244 and GR253.

The STC5420 accepts 12 clock reference inputs and generates 10 synchronized clock outputs: CLK1~CLK8, frame pulse clock CLK8K at 8kHz, and frame pulse clock CLK2K at 2kHz. CLK1~CLK8 may be programmed for wide variety of frequencies from 1MHz up to 156.25MHz, in 1kHz steps. Reference inputs are individually monitored for activity and quality. Reference selection may be automatic, manual, and hard-wired manual.

Two independent timing generators, T0 and T4, may operate in the *Freerun*, *Synchronized*, *Pseudo Holdover*, and *Holdover* mode. Each timing generator includes a DSP-based PLL. Synchronized mode external timing while freerun and holdover mode are self-timing. T0 supports Master/Slave and Multiple Master operation for redundant design. T4 only supports master operation. DSP-based PLL technology removes any external component except the oscillator. It provides excellent performance and reliability to STC5420.

The STC5420 is clocked by an external oscillator (TCXO or OCXO). Using a well-chosen external oscillator ensures the STC5420 meet the required specification and standards.

## **Features**

- Complies with ITU-T G.813 Opt1/Opt2, G.8262 EEC Opt1/Opt2, Telcordia GR1244 and GR253 (Stratum3/4E/ 4/SMC)

- Two timing generators T0 and T4; T4 may lock to T0's synchronized output

- Supports Master/Slave and Multiple-Master redundant application (T0 timing generator only)

- Provides programmable compensation for phase delay between master and slave unit, in 0.1ns steps

- Accepts external oscillator at frequency of 10MHz, 12.8MHz, 19.2MHz,or 20MHz with programming

- Accepts 12 clock reference inputs

- Supports frequency auto detection or manually acceptable frequency for reference inputs. Each of them is monitored for activity and quality

- Automatic/manual/hard-wired manual reference select

- Outputs 10 synchronized clock outputs, including 2 frame pulse clocks CLK8K and CLK2K

- 10 clock synthesizers generate frequencies

- Programmable phase skew in synthesizer level

- Phase-align or hit-less reference locking/switching

- Programmable loop bandwidth, from 0.1Hz to 100Hz

- Supports bus interface: Intel, Motorola, Multiplex, SPI

- Single 3.3V operation

- IEEE 1149.1 JTAG boundary scan

- Available in TQFP100 package

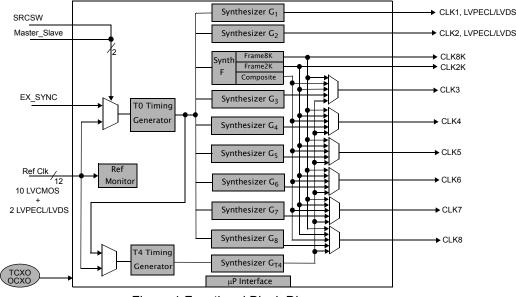

Figure 1:Functional Block Diagram

## **Table of Contents**

| STC5420 Pin Diagram (Top View)                      |    |

|-----------------------------------------------------|----|

| STC5420 Pin Description                             |    |

| Register Map                                        |    |

| Master Clock Frequency                              |    |

| Input and Output Frequencies                        |    |

| Input Frequencies                                   |    |

| Auto-Detect Acceptable Input Frequencies            |    |

| Manually Acceptable Input Frequencies               | 13 |

| Clock Output Frequencies                            | 14 |

| Clock Output Jitter                                 |    |

| General Description                                 |    |

| Application                                         |    |

| Overview                                            |    |

| Chip Master Clock                                   |    |

| Reference Inputs                                    |    |

| Timing Generators and Operation Modes               | 16 |

| Phase Synchronization                               |    |

| Clock Outputs                                       |    |

| Redundant Designs                                   |    |

| Control Interfaces                                  | 18 |

| Field Upgradability                                 |    |

| Advantage and Performance                           | 18 |

| Detailed Description                                | 19 |

| Chip Master Clock                                   | 19 |

| Freerun Clock                                       | 19 |

| Operation Mode                                      | 19 |

| PLL Event In                                        | 20 |

| Frequency and Phase Transients                      | 20 |

| Frequency Transients                                | 20 |

| Phase Transients                                    | 20 |

| History of Fractional Frequency Offset              | 20 |

| Short-Term History                                  | 20 |

| Long-Term History                                   | 21 |

| Device Holdover History                             | 21 |

| User-Specified History                              |    |

| Phase-Locked Loop Status Details                    | 21 |

| Reference Inputs Details                            | 22 |

| Acceptable Frequency and Frequency Offset Detection | 22 |

| Activity Monitoring                                 | 22 |

| Input Qualification                                 | 23 |

| Automatic Reference Election Mechanism              | 23 |

| Automatic Reference Selection                       | 24 |

| Manual Reference Selection Mode                     | 24 |

| Hard-wired Manual Reference Selection               | 24 |

| Clock Outputs Details                               | 24 |

| Clock Synthesizers                                  |    |

| Clock Generators                                    |    |

| Clock Output Phase Alignment                        |    |

| Synthesizer Skew Programming                        | 25 |

# Synchronous Clock for SETS Data sheet

| Clock Outputs                       | 25 |

|-------------------------------------|----|

| Redundant Application               | 26 |

| External Frame Reference Input      | 26 |

| Multiple Master Configuration       | 27 |

| Event Interrupts                    | 27 |

| Field Upgradability                 | 27 |

| Processor Interface Descriptions    |    |

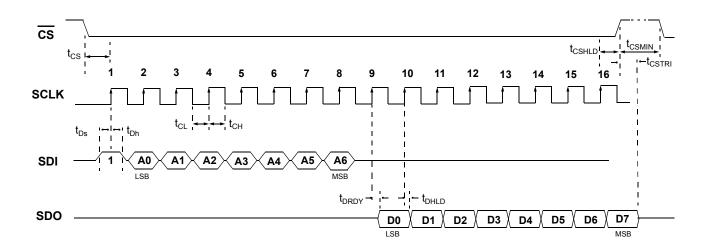

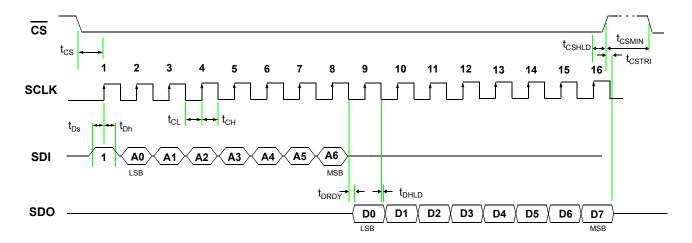

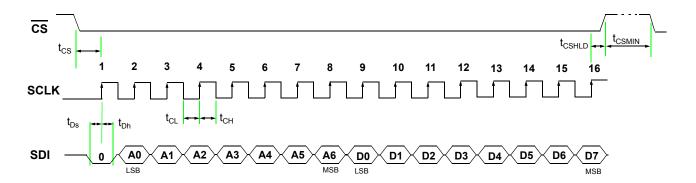

| SPI Bus Mode                        |    |

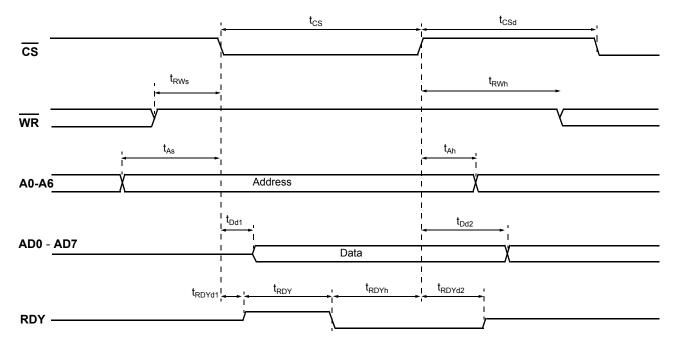

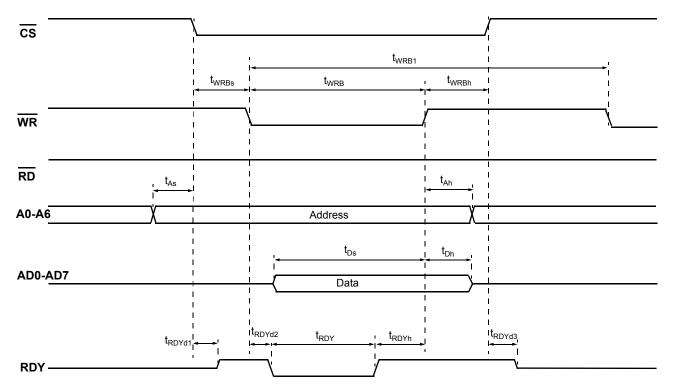

| Motorola Bus Mode                   |    |

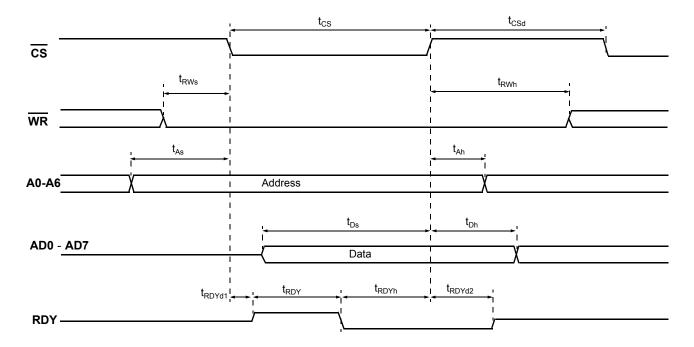

| Intel Bus Mode                      |    |

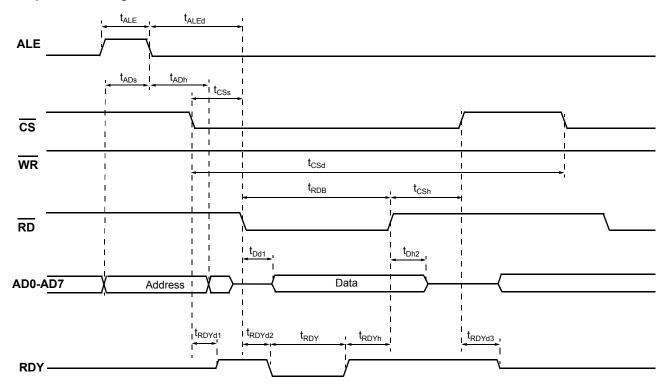

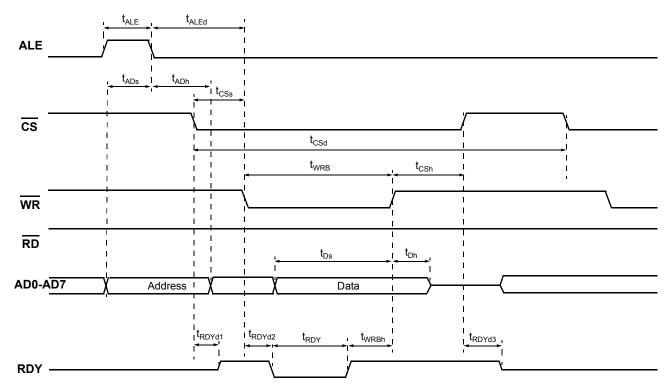

| Multiplex Bus Mode                  |    |

| Register Descriptions and Operation |    |

| General Register Operation          |    |

| Multibyte register reads            |    |

| Multibyte register writes           |    |

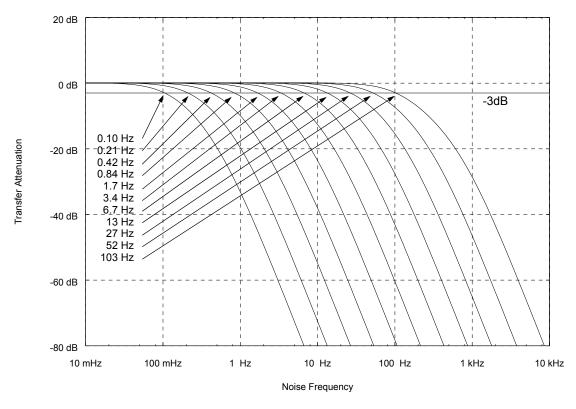

| Noise Transfer Functions            |    |

| Order Information                   |    |

| Specification Modification          |    |

| Application Notes                   |    |

| General                             |    |

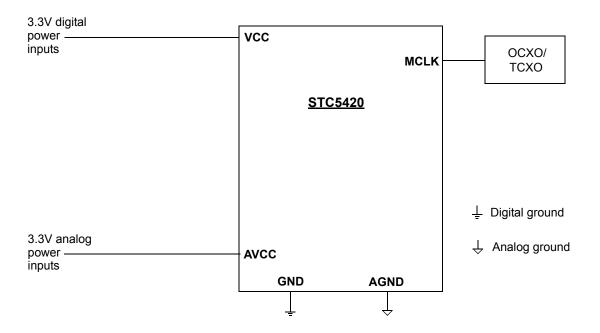

| Power and Ground                    |    |

| Master Oscillator                   |    |

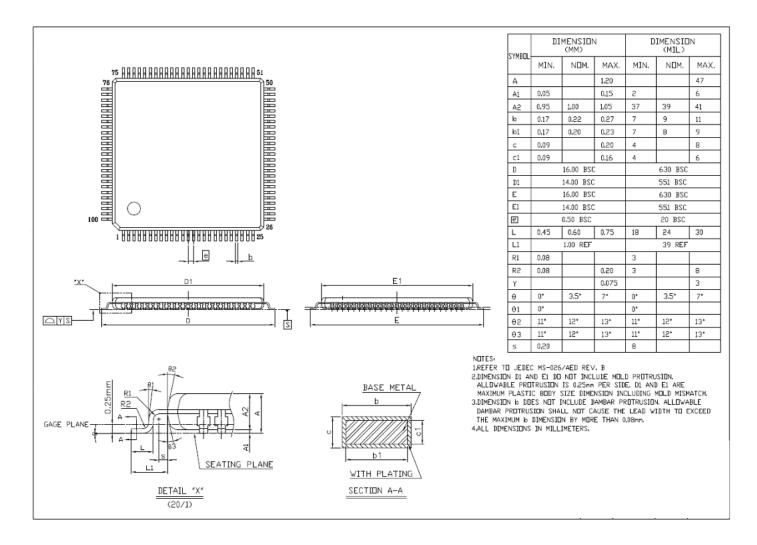

| Mechanical Specifications           |    |

| Revision History                    | 67 |

# Synchronous Clock for SETS Data sheet

## Table of Figures

| Figure 1: | Functional Block Diagram                      | 1  |

|-----------|-----------------------------------------------|----|

| Figure 2: | Activity Monitor                              | 22 |

| Figure 3: | Reference Qualification Scheme                | 23 |

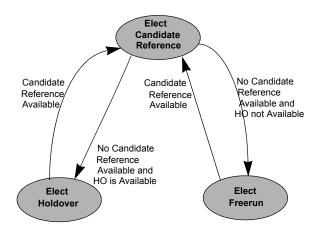

| Figure 4: | Automatic Reference Elector States            | 24 |

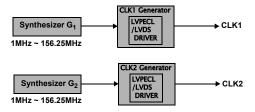

| Figure 5: | Output Clocks CLK1 and CLK2                   | 25 |

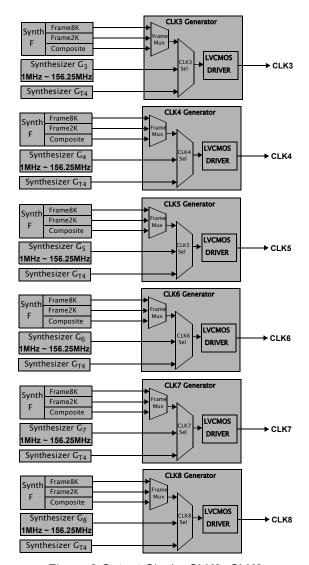

| Figure 6: | Output Clocks CLK3~CLK8                       | 25 |

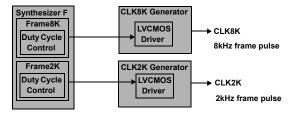

| Figure 7: | Output Clocks CLK8K and CLK2K                 | 26 |

| Figure 8: | SPI Bus, Read access (Pin CLKE = Low)         | 28 |

| Figure 9: | SPI Bus Timing, Read access (Pin CLKE = High) | 29 |

| Figure 10 | : SPI Bus Timing, Write access                | 29 |

| Figure 11 | : Motorola Bus Read Timing                    | 30 |

| Figure 12 | : Motorola Bus Write timing                   | 31 |

| Figure 13 | : Intel Bus Read Timing                       | 32 |

| Figure 14 | : Intel Bus Write Timing                      | 33 |

| Figure 15 | : Multiplex Bus Read Timing                   | 34 |

| Figure 16 | : Multiplex Bus Write Timing                  | 35 |

| Figure 17 | : Noise Transfer Functions                    | 62 |

| Figure 18 | : Power and Ground                            | 65 |

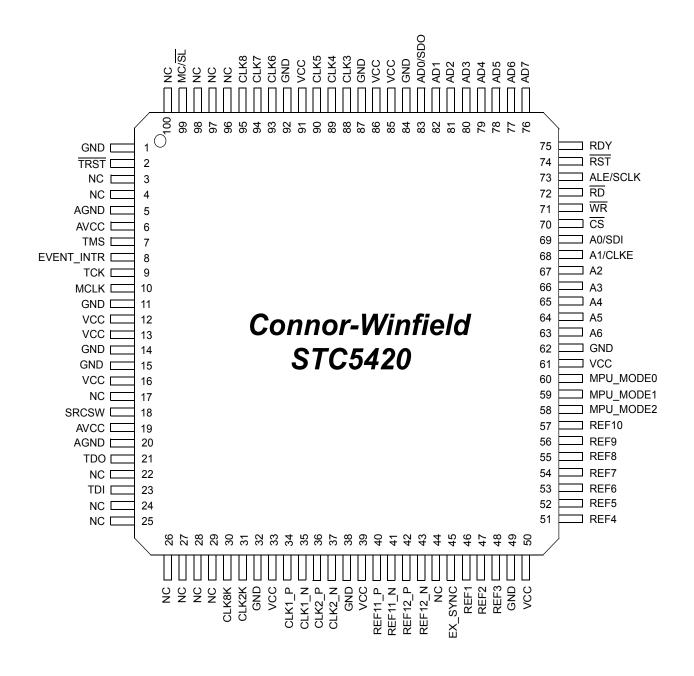

## STC5420 Pin Diagram (Top View)

Page 5 of 70 Rev:2.0 Date: September 28, 2011

# STC5420 Pin Description

All I/O is LVCMOS, except for CLK1 and CLK2 are LVPECL/LVDS. REF11 and REF12 are LVPECL/LVDS.

**Table 1: Pin Description**

| Pin Name   | Pin #                                                 | I/O | Description                                           |  |  |  |

|------------|-------------------------------------------------------|-----|-------------------------------------------------------|--|--|--|

| AVCC       | 6,19,                                                 |     | 3.3V analog power input                               |  |  |  |

| AGND       | 5, 20                                                 |     | Analog ground                                         |  |  |  |

| VCC        | 12, 13,<br>16, 33,<br>39, 50,<br>61, 85,<br>86, 91    |     | 3.3V digital power input                              |  |  |  |

| GND        | 1, 11, 14,<br>15, 32,<br>38, 49,<br>62, 84,<br>87, 92 |     | Digital ground                                        |  |  |  |

| TRST       | 2                                                     | 1   | JTAG boundary scan reset, active low                  |  |  |  |

| TCK        | 9                                                     | I   | JTAG boundary scan clock                              |  |  |  |

| TMS        | 7                                                     | - 1 | JTAG boundary scan mode selection                     |  |  |  |

| TDI        | 23                                                    | I   | JTAG boundary scan data input                         |  |  |  |

| TDO        | 21                                                    | 0   | JTAG boundary scan data output                        |  |  |  |

| RST        | 74                                                    | I   | Active low to reset the chip                          |  |  |  |

| MCLK       | 10                                                    | I   | Master clock input (TCXO or OCXO)                     |  |  |  |

| EVENT_INTR | 8                                                     | 0   | Event interrupt                                       |  |  |  |

| MC/SL      | 99                                                    | - 1 | Select master or slave mode for T0                    |  |  |  |

| EX_SYNC    | 45                                                    | 1   | Frame Sync signal                                     |  |  |  |

| REF1       | 46                                                    | _   | Reference input 1                                     |  |  |  |

| REF2       | 47                                                    | - 1 | Reference input 2                                     |  |  |  |

| REF3       | 48                                                    | 1   | Reference input 3                                     |  |  |  |

| REF4       | 51                                                    | - 1 | Reference input 4                                     |  |  |  |

| REF5       | 52                                                    | ı   | Reference input 5                                     |  |  |  |

| REF6       | 53                                                    | I   | Reference input 6                                     |  |  |  |

| REF7       | 54                                                    | - 1 | Reference input 7                                     |  |  |  |

| REF8       | 55                                                    | ı   | Reference input 8                                     |  |  |  |

| REF9       | 56                                                    | I   | Reference input 9                                     |  |  |  |

| REF10      | 57                                                    | Ţ   | Reference input 10                                    |  |  |  |

| REF11_P    | 40                                                    | Ţ   | Differential reference input 11 positive(LVPECL/LVDS) |  |  |  |

| REF11_N    | 41                                                    | I   | Differential reference input 11 negative(LVPECL/LVDS) |  |  |  |

| REF12_P    | 42                                                    | I   | Differential reference input 12 positive(LVPECL/LVDS) |  |  |  |

## Table 1: Pin Description

| Pin Name      | Pin # | I/O | Description                                                                                                                                                                               |  |

|---------------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REF12_N       | 43    | I   | Differential reference input 12 negative(LVPECL/LVDS)                                                                                                                                     |  |

| CLK1_P        | 34    | 0   | Clock output CLK1 positive. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $\rm G_1$ LVPECL or LVDS                                                                                   |  |

| CLK1_N        | 35    | 0   | Clock output CLK1 negative, 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer G <sub>1</sub> LVPECL or LVDS                                                                              |  |

| CLK2_P        | 36    | 0   | Clock output CLK2 positive. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $\rm G_2$ LVPECL or LVDS                                                                                   |  |

| CLK2_N        | 37    | 0   | Clock output CLK2 negative. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $\rm G_2$ LVPECL or LVDS                                                                                   |  |

| CLK3          | 88    | 0   | Clock output CLK3. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $G_3$ or Synthesizer $G_{T4}$ (T4); 2kHz, 8kHz or proprietary composite signal from Synthesizer F. LVCMOS.          |  |

| CLK4          | 89    | 0   | Clock output CLK4. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $G_4$ or Synthesizer $G_{T4}$ (T4); 2kHz, 8kHz or proprietary composite signal from Synthesizer F. LVCMOS.          |  |

| CLK5          | 90    | 0   | Clock output CLK5. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $G_5$ , or Synthesizer $G_{T4}(T4)$ ; 2kHz, 8kHz or proprietary composite signal from Synthesizer F. LVCMOS.        |  |

| CLK6          | 93    | 0   | Clock output CLK6. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $G_6$ or Synthesizer $G_{T4}$ (T4); 2kHz, 8kHz, or proprietary composite signal from Synthesizer F. LVCMOS.         |  |

| CLK7          | 94    | 0   | Clock output CLK7. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $\rm G_7$ or Synthesizer $\rm G_{T4}$ (T4); 2kHz, 8kHz, or proprietary composite signal from Synthesizer F. LVCMOS. |  |

| CLK8          | 95    | 0   | Clock output CLK8. 1MHz to 156.25MHz, in 1kHz steps, from Synthesizer $G_8$ or Synthesizer $G_{T4}$ (T4); 2kHz, 8kHz, or proprietary composite signal from Synthesizer F. LVCMOS.         |  |

| CLK8K         | 30    | 0   | 8kHz frame pulse signal, 50% duty cycle or programmable pulse width (T0)                                                                                                                  |  |

| CLK2K         | 31    | 0   | 2kHz frame pulse signal, 50% duty cycle or programmable pulse width (T0)                                                                                                                  |  |

| SRCSW         | 18    | ı   | Hard-wired manual reference pre-selection                                                                                                                                                 |  |

| MPU_MODE0     | 60    | I   | Bus interface: Intel, Motorola, Multiplex, SPI                                                                                                                                            |  |

| MPU_MODE1     | 59    | I   |                                                                                                                                                                                           |  |

| MPU_MODE2     | 58    | I   |                                                                                                                                                                                           |  |

| <del>CS</del> | 70    | ı   | SPI bus chip select                                                                                                                                                                       |  |

| WR            | 71    | I   | Write access for Intel, Motorola and Multiplex bus interface                                                                                                                              |  |

| RD            | 72    | I   | Read access for Intel and Multiplex bus interface                                                                                                                                         |  |

| ALE/SCLK      | 73    | I   | ALE: Address latch enable for Multiplex bus interface SCLK: Clock edge selection for SPI                                                                                                  |  |

| RDY           | 75    | 0   | Ready/Data Acknowledge for Intel, Motorola and Multiplex bus interface                                                                                                                    |  |

## **Table 1: Pin Description**

| Pin Name | Pin #                                                                       | I/O | Description                                              |

|----------|-----------------------------------------------------------------------------|-----|----------------------------------------------------------|

| A0/SDI   | 69                                                                          | I   | A0~A6: Address pins for bus interface Intel and Motorola |

| A1/CLKE  | 68                                                                          | I   | SDI: SPI bus data input                                  |

| A2       | 67                                                                          | I   | ·                                                        |

| A3       | 66                                                                          | I   | CLKE: Clock edge selection for SPI                       |

| A4       | 65                                                                          | I   |                                                          |

| A5       | 64                                                                          | I   |                                                          |

| A6       | 63                                                                          | I   |                                                          |

| AD0/SDO  | 83                                                                          | I/O | AD0~AD7: Bus interface Intel and Motorola data pins      |

| AD1      | 82                                                                          | I/O | Multiplex data and address pins                          |

| AD2      | 81                                                                          | I/O | SDO: SPI bus data output                                 |

| AD3      | 80                                                                          | I/O |                                                          |

| AD4      | 79                                                                          | I/O |                                                          |

| AD5      | 78                                                                          | I/O |                                                          |

| AD6      | 77                                                                          | I/O |                                                          |

| AD7      | 76                                                                          | I/O |                                                          |

| NC       | 3, 4, 17,<br>22, 24,<br>25, 26,<br>27, 28,<br>29, 44,<br>96, 97,<br>98, 100 |     | No connection. Pins are recommended to be tied to ground |

## **Register Map**

## **Table 2: Register Map**

| Addr              | Reg Name                         | Bits | Туре | Description                                                                              |

|-------------------|----------------------------------|------|------|------------------------------------------------------------------------------------------|

| 0x00              | Chip_ID                          | 15-0 | R    | Chip ID = 0x5420                                                                         |

| 0x01              |                                  |      |      |                                                                                          |

| 0x02              | Chip_Rev                         | 7-0  | R    | Chip revision number                                                                     |

| 0x03              | Chip_Sub_Rev                     | 7-0  | R    | Chip sub-revision number                                                                 |

| 0x04              | T0_M/S_Sts                       | 0    | R    | Indicates T0 master/slave state                                                          |

| 0x05              | T0_Slave_Phase_Adj               | 15-0 | R/W  | T0 slave phase adjust, 2's complement, step in 0.1ns                                     |

| 0x06              |                                  |      |      |                                                                                          |

| 0x07              | Fill_Obs_Window                  | 3-0  | R/W  | Activity monitor: Leaky bucket fill observation window                                   |

| 0x08              | Leak_Obs_Window                  | 3-0  | R/W  | Activity monitor: Leaky bucket leak observation window                                   |

| 0x09              | Bucket_Size                      | 5-0  | R/W  | Activity monitor: Leaky bucket size                                                      |

| 0x0A              | Assert_Threshold                 | 5-0  | R/W  | Activity monitor: Leaky bucket alarm assert threshold                                    |

| 0x0B              | De_Assert_Threshold              | 5-0  | R/W  | Activity monitor: Leaky bucket alarm de-assert threshold                                 |

| 0x0C              | Freerun_Cali                     | 10-0 | R/W  | Freerun calibration, 2's complement, -102.4 to +102.3ppm, step in                        |

| 0x0D              |                                  |      |      | 0.1ppm                                                                                   |

| 0x0E              | Disqualification_Range           | 9-0  | R/W  | Reference disqualification range, 0 ~102.3ppm. The value is also                         |

| 0x0F              |                                  |      |      | specified as pull-in range                                                               |

| 0x10              | Qualification_Range              | 9-0  | R/W  | Reference qualification range, 0 ~102.3ppm.                                              |

| 0x11              |                                  |      |      |                                                                                          |

| 0x12              | Qualification_Soaking_Time       | 5-0  | R/W  | Reference qualification soaking time, 0 ~63s                                             |

| 0x13              | Ref_Index_Selector               | 3-0  | R/W  | Select a reference input to access the register Ref_Info and Ref_Acceptable_Freq.        |

| 0x14              | Ref_Info                         | 15-0 | R    | Frequency offset and frequency info of the reference selected by                         |

| 0x15              |                                  |      |      | register Ref_Index_Selector                                                              |

| 0x16              | Ref_Activity                     | 12-0 | R    | Reference activity for reference 1 to 12 and cross ref                                   |

| 0x17              |                                  |      |      |                                                                                          |

| 0x18              | Ref_Qual                         | 11-0 | R    | Reference 1 ~ 12 qualification                                                           |

| 0x19              |                                  |      |      |                                                                                          |

| 0x1A              | Interrupt_Event_Status           | 7-0  | R/W  | Interrupt events                                                                         |

| 0x1B              | Interrupt_Event_Enable           | 7-0  | R/W  | Selects which of interrupt events will assert pin EVENT_INTR                             |

| 0x1C              | Interrupt_Config                 | 1-0  | R/W  | Pin EVENT_INTR configuration and idle mode                                               |

| 0x1D              | Hard-Wired_Switch_Pre_Selections | 7-0  | R/W  | Pre-selected reference number 1 and reference number 2 for hard-wired manual switch mode |

| 0x1E              | SRCSW_Status                     | 0    | R    | Indicates the status of pin SRCSW                                                        |

| 0x1F <sup>1</sup> | T0/T4_Tag_Select                 | 0    | R/W  | Selects registers between T0 and T4 for register 0x20 - 0x3F                             |

| 0x20              | Control_Mode                     | 7-2  | R/W  | Holdover history usage, Revertive, Manual/Auto, OOP, Slave inherit, SRCSW                |

| 0x21              | Loop_Bandwidth                   | 7-0  | R/W  | Loop bandwidth selection                                                                 |

| 0x22              | Auto_Elect_Ref                   | 3-0  | R    | Indicates the reference elected by auto reference elector                                |

| 0x23              | Manual_Select_Ref                | 3-0  | R/W  | The reference specified by users for manual selection mode                               |

| 0x24              | Selected_Ref                     | 3-0  | R    | Indicates the PLL current selected reference                                             |

## Table 2: Register Map

| Addr | Reg Name                | Bits | Туре | Description                                                                                                                                           |

|------|-------------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x25 | Device_Holdover_History | 31-0 | R    | Device Holdover History                                                                                                                               |

| 0x26 |                         |      |      |                                                                                                                                                       |

| 0x27 |                         |      |      |                                                                                                                                                       |

| 0x28 |                         |      |      |                                                                                                                                                       |

| 0x29 | Long_Term_Accu_History  | 31-0 | R    | Long term Accumulated History                                                                                                                         |

| 0x2A |                         |      |      |                                                                                                                                                       |

| 0x2B |                         |      |      |                                                                                                                                                       |

| 0x2C |                         |      |      |                                                                                                                                                       |

| 0x2D | Short_Term_Accu_History | 31-0 | R    | Short term Accumulated History                                                                                                                        |

| 0x2E |                         |      |      |                                                                                                                                                       |

| 0x2F |                         |      |      |                                                                                                                                                       |

| 0x30 |                         |      |      |                                                                                                                                                       |

| 0x31 | User_Specified_History  | 31-0 | R/W  | User programmed holdover history                                                                                                                      |

| 0x32 |                         |      |      |                                                                                                                                                       |

| 0x33 |                         |      |      |                                                                                                                                                       |

| 0x34 |                         |      |      |                                                                                                                                                       |

| 0x35 | History_Ramp            | 7-0  | R/W  | Control long term history and short term history accumulation bandwidth and the locking stage's frequency ramp control                                |

| 0x36 | Ref_Priority_Table      | 47-0 | R/W  | REF1-12 selection priority                                                                                                                            |

| 0x37 |                         |      |      |                                                                                                                                                       |

| 0x38 |                         |      |      |                                                                                                                                                       |

| 0x39 |                         |      |      |                                                                                                                                                       |

| 0x3A |                         |      |      |                                                                                                                                                       |

| 0x3B |                         |      |      |                                                                                                                                                       |

| 0x3C | PLL_Status              | 7-0  | R    | PLL status: SYNC, LOS, LOL, OOP, SAP, FEE, DHT, HHA                                                                                                   |

| 0x3D | Holdover_Accu_Flush     | 0    | W    | Flush/reset the long-term history and the device holdover history                                                                                     |

| 0x3E | PLL_Event_Out           | 7-0  | R/W  | PLL event out (Reserved)                                                                                                                              |

| 0x3F | PLL_Event_In            | 7-0  | R/W  | PLL event in: Relock                                                                                                                                  |

| 0x40 | EX_SYNC_Edge_Config     | 0    | R/W  | Select framing edge for EX_SYNC (falling or rising edge)                                                                                              |

| 0x41 | Slave_Frame_Align       | 3-0  | R/W  | Select cross ref source and frame edge for slave T0 timing generator                                                                                  |

| 0x42 | Master_Frame_Align      | 47-0 | R/W  | To timing generator selects the frame phase alignment and frame                                                                                       |

| 0x43 |                         |      |      | alignment working manner in master mode. Not for T4 timing generator.                                                                                 |

| 0x44 |                         |      |      | ator.                                                                                                                                                 |

| 0x45 |                         |      |      |                                                                                                                                                       |

| 0x46 |                         |      |      |                                                                                                                                                       |

| 0x47 |                         |      |      |                                                                                                                                                       |

| 0x4A | Synth_Index_Select      | 3-0  | R/W  | Determine which synthesizer is selected for setting frequency value at register Synth_Freq_Value and adjusting phase skew at registers Synth_Skew_Adj |

| 0x4B | Synth_Freq_Value        | 17-0 | R/W  | Selects synthesizer frequency value from 1MHz to 156.25MHz, in                                                                                        |

| 0x4C |                         |      |      | 1kHz steps, based on which synthesizer index is selected at the register Synth, leday, Select                                                         |

| 0x4D |                         |      |      | ister Synth_Index_Select                                                                                                                              |

| 0x4E | Synth_Skew_Adj          | 11-0 | R/W  | Adjust phase skew for the synthesizer with the index selected at                                                                                      |

| 0x4F |                         |      |      | register Synth_Index_Select                                                                                                                           |

## **Table 2: Register Map**

| Addr | Reg Name             | Bits | Туре | Description                                                              |

|------|----------------------|------|------|--------------------------------------------------------------------------|

| 0x50 | CLK1/2_Signal_Level  | 1-0  | R/W  | Select the signal level (LVDS or LVPECL) for clock outputs CLK1 and CLK2 |

| 0x51 | CLK1_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK1                          |

| 0x52 | CLK2_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK2                          |

| 0x53 | CLK3_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK3                          |

| 0x54 | CLK4_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK4                          |

| 0x55 | CLK5_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK5                          |

| 0x56 | CLK6_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK6                          |

| 0x57 | CLK7_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK7                          |

| 0x58 | CLK8_Sel             | 1-0  | R/W  | Select synthesizer or enable tri-state for CLK8                          |

| 0x59 | Frame8K_Sel          | 6-0  | R/W  | 8kHz frame pulse clock duty cycle selection, signal inversion            |

| 0x5A | Frame2K_Sel          | 6-0  | R/W  | 2kHz frame pulse clock duty cycle selection, signal inversion            |

| 0x5B | Ref_Acceptable_Freq  | 14-0 | R/W  | Select integer N for manually acceptable frequency at Nx8kHz;            |

| 0x5C |                      |      |      | Enable auto detection of reference input frequency                       |

| 0x5D | Frame_Mux            | 11-0 | R/W  | Select one of frame signal (Frame8K, Frame2K, or composite sig-          |

| 0x5E |                      |      |      | nal) and forward it to CLK3~CLK8 selection individually                  |

| 0x5F | Diff_REF_Polarity    | 1-0  | R/W  | Differential input REF(11~12)_P and REF(11~12)_N polarity reverse        |

| 0x70 | Field_Upgrade_Status | 2-0  | R    | Indicates the status of field upgrade process                            |

| 0x71 | Field_Upgrade_Data   | 7-0  | R/W  | Load 7600 bytes of firmware configuration data                           |

| 0x72 | Field_Upgrade_Count  | 12-0 | R    | Count byte numbers that have been loaded                                 |

| 0x73 |                      |      |      |                                                                          |

| 0x74 | Field_Upgrade_Start  | 7-0  | W    | Write three values consecutively to start the field upgrade process      |

| 0x7F | MCLK_Freq_Reset      | 7-0  | R/W  | Select the frequency of the external oscillator                          |

Note 1: Timing generator T0 and T4 share register  $0x20 \sim 0x3F$ . Register 0x1F selects between T0 and T4 for the sharing registers  $0x20 \sim 0x3F$ .

# **Master Clock Frequency**

The STC5420 supports four different frequencies of master clock: 10MHz, 12.8MHz, 19.2MHz, and 20MHz. See Chip Master Clock for details. Initial default accepted frequency of MCLK is 12.8MHz.

**Table 3: Master Clock Frequency**

| 12.8MHz (Initial default frequency) |  |  |  |  |  |

|-------------------------------------|--|--|--|--|--|

| 10MHz                               |  |  |  |  |  |

| 19.2MHz                             |  |  |  |  |  |

| 20MHz                               |  |  |  |  |  |

## **Input and Output Frequencies**

## **Input Frequencies**

### **Auto-Detect Acceptable Input Frequencies**

The STC5420 can automatically detect the frequency of the reference input when the user enable the autodetect function at the register **Ref Index Selector** and **Ref Acceptable Freq** for REF1~REF12 individually. REF11 and REF12 are LVPECL/LVDS. The acceptable frequency for auto detection is shown in Table 4.

**Table 4: Auto-Detect Acceptable Ref Input Frequencies**

| Reference Input      | Frequency                                                                |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------|--|--|--|--|--|

|                      | 8 kHz                                                                    |  |  |  |  |  |

|                      | 64 kHz                                                                   |  |  |  |  |  |

|                      | 19.44 MHz                                                                |  |  |  |  |  |

|                      | 38.88 MHz                                                                |  |  |  |  |  |

|                      | 77.76 MHz                                                                |  |  |  |  |  |

| REF1 ~ REF 12        | 1.544 MHz                                                                |  |  |  |  |  |

|                      | 2.048 MHz                                                                |  |  |  |  |  |

|                      | 6.48 MHz                                                                 |  |  |  |  |  |

|                      | 8.192 MHz                                                                |  |  |  |  |  |

|                      | 16.384 MHz                                                               |  |  |  |  |  |

|                      | 25 MHz                                                                   |  |  |  |  |  |

|                      | 50 MHz                                                                   |  |  |  |  |  |

|                      | 125 MHz                                                                  |  |  |  |  |  |

| REF7 <sup>2</sup>    | Proprietary Composite signal                                             |  |  |  |  |  |

| EX_SYNC <sup>3</sup> | Proprietary Composite signal,<br>2kHz or 8kHz external frame sync inputs |  |  |  |  |  |

## Manually Acceptable Input Frequencies

STC5420 provides another option which allows the user to select the manually acceptable reference frequency for REF1~REF12 individually, at the integer multiple of 8kHz (Nx8kHz, N is integer from 1 to 32767). Hence the manually acceptable reference frequency range is 8kHz to 262.136MHz, in 8kHz steps. When a manually acceptable reference frequency is used, the user need to access the register **Ref Acceptable Freq** to set the integer N for associated reference input selected at the register **Ref Index Selector**.

#### Input Frequency = $N \times 8kHz$ , where $N = 1 \sim 32767$

Note 2

In slave mode configuration, REF7 can also accept proprietary composite signal as input besides the high frequencies shown in Figure 3.

Note 3:

In both master and slave mode configuration, EX\_SYNC may accept proprietary composite signal and 2kHz or 8kHz external frame reference inputs.

## **Clock Output Frequencies**

## **Table 5: Available Clock Output Frequencies**

| CLK   | CLK Level   | Synthesizer                           | Clock Output Frequency Range                                  |

|-------|-------------|---------------------------------------|---------------------------------------------------------------|

| CLK1  | LVPECL/LVDS | G <sub>1</sub>                        | 1MHz ~ 156.25MHz, in 1kHz steps                               |

| CLK2  | LVPECL/LVDS | G <sub>2</sub>                        | 1MHz ~ 156.25MHz, in 1kHz steps                               |

| CLK8K | 11/01/00    | F                                     | Frame8K at 8kHz                                               |

| CLK2K | LVCMOS      | F                                     | Frame2K at 2kHz                                               |

| CLK3  | LVCMOS      | G <sub>3</sub> , F or G <sub>T4</sub> | 1MHz ~ 156.25MHz, in 1kHz steps; Frame8K/Frame2K at 8kHz/2kHz |

| CLK4  | LVCMOS      | G <sub>4</sub> , F or G <sub>T4</sub> | 1MHz ~ 156.25MHz, in 1kHz steps; Frame8K/Frame2K at 8kHz/2kHz |

| CLK5  | LVCMOS      | G <sub>5</sub> , F or G <sub>T4</sub> | 1MHz ~ 156.25MHz, in 1kHz steps; Frame8K/Frame2K at 8kHz/2kHz |

| CLK6  | LVCMOS      | G <sub>6</sub> , F or G <sub>T4</sub> | 1MHz ~ 156.25MHz, in 1kHz steps; Frame8K/Frame2K at 8kHz/2kHz |

| CLK7  | LVCMOS      | G <sub>7</sub> , F or G <sub>T4</sub> | 1MHz ~ 156.25MHz, in 1kHz steps; Frame8K/Frame2K at 8kHz/2kHz |

| CLK8  | LVCMOS      | G <sub>8</sub> , F or G <sub>T4</sub> | 1MHz ~ 156.25MHz, in 1kHz steps; Frame8K/Frame2K at 8kHz/2kHz |

# **Clock Output Jitter**

**Table 6: Clock Output Jitter**

| Clock Output               | Frequency | RMS jitter <sup>4</sup><br>(Typical) | pk-pk jitte<br>(Typ | er <sup>4</sup> (10 <sup>-12</sup> )<br>ical) |

|----------------------------|-----------|--------------------------------------|---------------------|-----------------------------------------------|

|                            | (MHz)     | (ps)                                 | (ps)                | (UI)                                          |

|                            | 156.25    | 13                                   | 210                 | 0.03                                          |

|                            | 155.52    | 13                                   | 210                 | 0.03                                          |

| CLK1/CLK2<br>(LVPECL/LVDS) | 125       | 13                                   | 210                 | 0.03                                          |

|                            | 77.76     | 13                                   | 210                 | 0.02                                          |

|                            | 77.76     | 19                                   | 330                 | 0.03                                          |

|                            | 38.88     | 16.5                                 | 280                 | 0.01                                          |

| CLK3~CLK7                  | 19.44     | 15                                   | 230                 | 0.005                                         |

| (LVCMOS)                   | 25        | 13                                   | 180                 | 0.005                                         |

|                            | 2.048     | 11                                   | 180                 | 0.0004                                        |

|                            | 1.544     | 11                                   | 160                 | 0.0003                                        |

Note 4: Filter bandwidth is from 12kHz to Frequency/2

## **General Description**

## **Application**

The STC5420 is a single chip solution for the synchronous clock in SDH (SETS), SONET, and Synchronous Ethernet network elements. The device is fully compliant with ITU-T G.813 (option1 and option2), G.8262 EEC (option1 and option2), Telcordia GR1244, and GR253 (Stratum3/4E/4/SMC). Its highly integrated design implements all necessary reference selection, monitoring, filtering, synthesis, and control functions. An external oscillator (e.g., high precision OCXO or TCXO) completes a system level solution (see Functional Block Diagram, Figure 1). The STC5420 has four programmable frequency options of external oscillator. The STC5420 supports master/slave and multiple-master operations for redundant application.

## Overview

The STC5420 accepts 12 reference inputs and generates 10 synchronized clock outputs, including 2 frame pulse clock outputs CLK8K and CLK2K at 8kHz and 2kHz. Two independent PLL-based timing generators, T0 and T4, provide the essential functions for Synchronous Equipment Timing Sources (SETS). T0 controls synthesizers  $G_1 \sim G_8$ , and synthesizer F. T4 controls synthesizer  $G_{T4}$ . Clock outputs CLK1 $\sim$ CLK8 can be derived from synthesizer  $G_1 \sim G_8$ , respectively. CLK3 $\sim$ CLK8 can also be derived from synthesizer F through T0 path or synthesizer  $G_{T4}$  through T4 path. Frame pulse clock outputs are derived from synthesizer F. The STC5420 incorporates a microprocessor interface, which can be configured for all common microprocessor interface types.

## **Chip Master Clock**

The STC5420 operates with an external oscillator (e.g., OCXO or TCXO) as its master clock. The device supports four different frequencies of master clock: 10MHz, 12.8MHz, 19.2MHz, and 20MHz. Initial default accepted frequency is 12.8MHz.

## **Reference Inputs**

The STC5420 accepts 12 reference inputs. REF11 and REF12 are LVPECL/LVDS, remaining 10 are LVCMOS. The 12 reference inputs are continuously

activity and quality monitored. The reference inputs may be selected to accept either the auto-detect acceptable reference frequency which can be auto-matically detected by STC5420 or manually acceptable reference frequency. The activity monitoring is implemented with a programmable leaky bucket algorithm.

A reference is designated as "qualified" if it is active and its fractional frequency offset is within the programmed range for a programmed soaking time. An auto reference elector elects the most appropriate one from the reference inputs according to the revertivity status, and each reference's priority and qualification. Revertivity determines whether a higher priority qualified reference should preempt a qualified current auto-elected reference. If none of the references input is qualified, holdover or freerun mode will be elected depending on the availability of the holdover history.

Reference selection may be automatic, manual, or hard-wired manual. In automatic reference selection mode, the most appropriate one elected from the auto reference elector will be the selected reference input. In manual reference selection mode, user may specify any of the reference inputs as the selected reference input for external timing or holdover/freerun for self-timing. In hard-wired manual mode, user can fast switch using control pin SRCSW between two preprogrammed reference inputs. The reference input elected from the auto reference elector will not affect the selected reference input in manual or hard-wired manual mode.

In manual reference selection mode, the timing generator T4 may accept T0's synchronized output as its input.

# Timing Generators and Operation Modes

The STC5420 includes two independent timing generates, T0 and T4, to provide the essential functions for SETS. Each timing generator can individually operate in *Freerun*, *Synchronized*, *Pseudo-Holdover* and *Holdover* mode. A timing generator is in either external-timing mode or self-timing mode. In external timing mode, PLL of the timing generator phase locks to the selected external reference input. In self-timing mode, the PLL simply tunes the clock

synthesizers to a given fractional frequency offset. Synchronized mode is in external timing. PLL's loop bandwidth may be programmed individually to vary the timing generator's filtering function. Conversely, freerun, pseudo-holdover and holdover modes are all in self-timing. When selected reference input and previous holdover history are unavailable, such as in system's initialization stage, freerun mode may be entered or used. When selected reference input is unavailable but a long-term holdover history accumulated in previous synchronized mode is available, holdover mode may be entered or used. STC5420 may enter pseudo-holdover using short-term frequency history. In STC5420, the freerun clock is derived from the MCLK (external oscillator) and digitally calibrated to compensate the external oscillator's accuracy offset. STC5420 also allow users to program and manipulate the holdover history accumulators.

## **Phase Synchronization**

In synchronized mode, the phase relationship between the selected reference input and the clock output may be phase arbitrary or frame phase align for T0 timing generator. For timing generator T4, the phase relationship is only phase arbitrary. Zero frame phase relationship is produced for T0 timing generator by programming as frame phase align mode. Switching to a new reference input may expect a longer pull-in process in this mode. On the other hand, programming as arbitrary mode, an arbitrary phase relationship incorporates phase rebuild on reference input switching to minimize the downstream clock's phase transient. In this scenario, the STC5420 can provide hit-less switching if both reference inputs are traced to the same clock source (e.g., PRC). The STC5420 may accept external frame reference to achieve frame alignment in frame phase align mode. The frame reference and the frame edge, and frame phase alignment mode may be configured independently for each individual reference input.

A maximum frequency ramp may be programmed to minimize the ramp of fractional frequency offset changing in the case that the new selected reference is not traced to the same source. This feature restrains the frequency transient which may cause the pull-out-of- lock of the downstream network elements.

## **Clock Outputs**

The STC5420 outputs 10 synchronized clock outputs: 2 differential clock outputs (LVPECL or LVDS) CLK1 and CLK2, 6 LVCMOS clock outputs CLK3 to CLK8 (LVCMOS), one CLK8K and one CLK2K frame pulse clock outputs (LVCMOS). CLK1~CLK8 can be derived from synthesizer  $G_1 \sim G_8$  through T0 path, respectively, in which CLK3~CLK8 can also be derived from synthesizer F through T0 path or synthesizer G<sub>T4</sub> through T4 path. See Figure 1 for functional details. Frequency of clock outputs CLK1~CLK8 is programmable by programing frequency of the associated synthesizer from 1MHz up to 156.25MHz, in 1kHz steps. Each of the synthesizers has different default frequency value. The STC5420 allows the user to program the phase skew of each clock synthesizer, up and down 50ns in roughly 0.024ns step to adjust the phase of clock outputs.

Frame pulse clock synthesizer F generates frame pulse clock Frame8K/Frame2K at frequency of 8kHz/2kHz and a proprietary composite signal which carries 8kHz clock, 2kHz frame, and the selected reference information. The duty-cycle of Frame8K and Frame2K is programmable. Clock outputs CLK8K and CLK2K are directly driven from Fram8K and Frame2K.

## **Redundant Designs**

Timing generator T0 supports **master/slave** and **multiple-master** operation for redundant applications to allow system protection against the failure of the single unit.

In master/slave configuration, the slave unit phase-locks and frame aligns (8kHz or 2kHz) to the cross-reference from the master unit, using highest available loop bandwidth and ignores any frequency ramp protection. The phase of slave's clock outputs may be adjusted up and down 3.2us, in 0.1ns step, to compensate for the propagation and re-transmission delay of the cross-couple path. This will then minimize the phase hits to the downstream devices resulting from master/slave switches.

In multiple-master configuration, all units work as masters and lock to the same reference input in parallel. With the help of frame phase align mode and the extra frame edge, clock outputs of all the units may keep in frame phase alignment. No phase compensa-

tion as in master/slave configuration. In order to meet same synchronization requirement, each unit should use same parameter setup including loop bandwidth. Multiple-master configuration demands a high quality external oscillator to obtain a precise frame phase alignment.

## **Control Interfaces**

The STC5420's controls interfaces are composed of hardwire control pins and the bus interface. They provide application access to the STC5420's internal control and status registers. This bus interface may be configured among four type of micro-controller interfaces, three of them are in parallel (Intel, Motorola, Multiplexed) and one in serial (SPI). The selection of the bus interface is pin-controlled.

## Field Upgradability

The STC5420 supports Field Upgradability which allows the user to load size of 7600 byte firmware configuration data (provided as per request) via bus interface. It provides the user a flexible field solution for different applications.

## **Advantage and Performance**

The kernel of each timing generator is a DSP-based PLL. In STC5420, all internal modules are either digital or numerical, including the phase detectors, filters, and clock synthesizers. The revolutionary pure-digital design makes the timing generator become an accurate and reliable deterministic system. This modern technology removes any external component except the external oscillator. It provides excellent performance and reliability to STC5420. A well-chosen oscillator will make STC5420 meet all the synchronization requirements. Short-term stability associated with the desired loop bandwidth is a more important factor than aging projection and thermal response when select an appropriate oscillator.

## **Detailed Description**

The STC5420 is a single chip solution for the synchronous clock in SDH (SETS), SONET, and Synchronous Ethernet network elements. The revolutionary pure-digital internal modules, DSP-based PLL and clock synthesizer are used in the device so that the overall characteristics are more stable compared to traditional method.

## **Chip Master Clock**

The device operates with an external oscillator (e.g., OCXO or TCXO) as its master clock, connected to the MCLK input, pin 10. Generally, user should select an oscillator has great stability and low phase noise as the master clock (MCLK).

The STC5420 supports four different accepted frequencies of master clock: 10MHz, 12.8MHz, 19.2MHz, and 20MHz. Initial default accepted frequency of MCLK for STC5420 is 12.8MHz. When 10MHz, 19.2MHz, or 20MHz is selected as the frequency of MCLK, the user must write register MCLK Freq Reset three times consecutively, with no intervening read/writes from/to other register. An internal soft-reset will occur after three writes completed. The accepted frequency of MCLK input returns to 12.8MHz following any regular reset. See register MCLK Freq Reset for details.

In the meantime, the STC5420 allows user to read three values at the register **MCLK Freq Reset**: FRQID, COUNT, and ID Written Value.

#### **FRQID**

Indicates the ID of the frequency of MCLK that the STC5420 currently accept.

#### COUNT

Indicates how many times the register **MCLK Freq Reset** has been written to.

## **ID Written Value**

Indicates the ID of associated value that is being written to the register **MCLK Freq Reset**.

See the register **MCLK Freq Reset** for more details.

## Freerun Clock

The STC5420 has an internal freerun clock synthesized from the MCLK. The frequency offset of the internal freerun clock can be calibrated by writing to the register **Freerun Cali**. It has the stability of the external TCXO/OCXO. The calibration offset may be programmed in 0.1ppm steps from -102.4 to +102.3ppm, in 2's complement. This feature allow the user can digitally calibrate the freerun clock without physically adjusting the local oscillator.

## **Operation Mode**

The STC5420 includes two timing generators, T0 and T4 timing generators. Each timing generator has its own PLL and can be individually operate in either external-timing or self-timing mode. In external timing mode, PLL of a timing generator phase-locks to a reference input. In self-timing mode, PLL simply operates with the external oscillator (MCLK). The STC5420 supports four operation modes: *freerun* (self-timing), *synchronized* (external-timing), *pseudo-holdover* (self-timing) and *holdover* (self-timing).

#### Freerun Mode

Freerun mode is typically used during system's initialization stage when none of reference inputs is available and the clock synchronization has not been achieved. The clock output generated from the STC5420 in freerun mode is based on the internal freerun clock which is synthesized from MCLK. Frequency of the internal freerun clock can be calibrated by writing to the register **Freerun Cali**.

#### **Synchronized Mode**

In synchronized mode, the built-in PLL of the timing generator locks to the selected reference input. Each timing generator's loop bandwidth is independently programmable from 0.1Hz to 100Hz by writing to the register **Loop Bandwidth**. The noise transfer function of the PLL is determined accordingly by the loop bandwidth and has maximum gain under 0.2dB. In synchronized mode, the phase relationship between the reference input and the clock output can be configured as arbitrary or aligned for timing generator T0 at register **Master Frame Align**. Timing generator T4 operates only in phase arbitrary.

## **Pseudo-Holdover Mode**

In pseudo-holdover mode, the clock is synthesized from the MCLK and an accumulated short-term his-

# STC5420 Synchronous Clock for SETS Data sheet

tory. This history is accumulated by a built in programmable short-term history accumulator consecutively, which presents the latest updated fractional frequency offset of the synchronous clock output of each timing generator. The user can read the short-term history from register **Short Term Accu History**.

#### **Holdover Mode**

Holdover mode is typically used when none of reference inputs is available and the holdover history has been built. In holdover mode, the frequency offset of the clock output is maintained closely to previous value generated when the selected reference input was valid. User can select either device holdover history or user specified holdover history at the register **Con-trol Mode** in holdover mode.

## **PLL Event In**

The STC5420 provides direct communication with the PLL's timing generator by writing to the register **PLL Event In**. Following events can be triggered:

Relock. PLL starts a relock process if this event is triggered. In frame phase align mode, PLL relocks to the reference input and the frame edge is re-selected as well. In phase arbitrary mode, PLL relocks to the reference input and restart the phase rebuild process.

## **Frequency and Phase Transients**

Severe frequency and phase transients of the clock output will cause lost of lock or buffer overflow/underflow on downstream circuit. By providing programmable maximum slew rate and phase rebuild function, both frequency and phase transient of the STC5420's clock output is controlled to minimize the impact on downstream circuits.

## **Frequency Transients**

The STC5420 smoothly control the frequency transient on the clock output. During reference input switching or operation mode switching (etc., switch to freerun or holdover mode), if the clock output prior to switching has different frequency offset than the desired clock output, it smoothly approaches to desired frequency offset with a maximum acceleration/decel- eration rate by writing to the register History Ramp. The maximum slew rate can be programmed as 1.0, 1.5, 2.0 ppm/second. With a limited acceleration/ deceleration, the pull-in process may last longer. However, it will minimize the frequency transient impact to the downstream clock and

ensure meeting components frequency impact tolerance

#### **Phase Transients**

The STC5420 minimize the variation of the phase transient on the clock output when a phase hit occurs on the selected reference input. The overshoot in the clock output's phase transient response will be a small amount under 2%.

During reference input switching or recovering from LOS/LOL condition, the phase transient is also occurred on the clock output. The STC5420 can minimize it with a phase rebuild function. In synchronized mode, the phase relationship between the reference input and the clock output can be programmed to phase arbitrary or frame phase align at the register **Master Frame Align**. If phase arbitrary is selected, a phase rebuild function is performed before locking to the new/recovered reference input. Hit-less switching is achieved with this function and the phase hit to downstream circuits is eliminated. If frame phase align is selected, the clock output is in frame phase alignment with the reference input. Only T0 timing generator supports frame phase alignment.

# History of Fractional Frequency Offset

The STC5420 monitors and tracks the fractional frequency offset between the clock output and MCLK. The history data of the frequency offset is used by clock synthesizers to generate desire outputs while the timing generator is pending for reference input availability. Two weighted 3<sup>rd</sup> order low-pass filter are used internally as two history accumulators: the short term history accumulator and the long term history accumulator. A mature long term history is stored and further updated as device holdover history. It is used when the STC5420 operates in holdover mode. In addition, the STC5420 allows user to program an user specified history as needed of the application.

### Short-Term History

Short-term history is an average frequency offset between the clock output and MCLK which is filtered internally using a weighted 3rd order low-pass filter with the small time constant. The -3dB filter response point can be programmed from 0.16Hz to 1.3Hz by writing to the register **History Ramp register**. Short-

# STC5420 Synchronous Clock for SETS Data sheet

term history can be read from the register **Short\_Term\_Accu\_History**. Typically, short-term history is used by clock synthesizer in two conditions: First, it is used in between the transition of two different operation modes; second, it is used if LOS occurs when the STC5420 operates in synchronized mode with manually reference selection. In addition, short-term history is provided to perform failure diagnostics and evaluations.

## **Long-Term History**

Long-term history is an average frequency offset between the clock output and MCLK which is filtered internally using a weighted 3rd order low-pass filter with the long time constant. The -3 dB filter response point can be programmed from 0.15mHz to 1.3Hz by writing to the register **History Ramp**. The history value can be read from the register **Long Term Accu History**.

#### **Device Holdover History**

Device holdover history is the history data used when the STC5420 runs in holdover mode. It is acquired from the long term history previously described. In synchronized mode, when timing generators PLL has locked to the selected reference input for over 15 minutes, the long term history is stored and further updated as the device holdover history. If LOS or LOL occurs, the device holdover history will stay at the latest updated value until re-enter the synchronized mode and the PLL locks to the replaced selected reference input for another 15 minutes. Set Bit HO\_Usage bit of the register **Control Mode** to select using device holdover history. Its value can be read from the register **Device Holdover History**.

#### **User-Specified History**

The STC5420 allows user to provide the history data created from their own sophisticated history accumulation algorithms by writing to the register **User Specified History**. Set bit HO\_Usage of the register **Control Mode** to select using user specified holdover history. Its value can be read from the register **User Specified History**.

## **Phase-Locked Loop Status Details**

The register **PLL Status** contains the detailed status of the PLLs, including the signal activity of the selected reference, the synchronization status, and the availability of the holdover histories.

#### SYNC bit

In external-timing mode, this bit indicates the achievement of synchronization. This bit will not be asserted in self-timing mode.

#### LOS bit

In external-timing mode, this bit indicates the loss of signal on the selected reference. This bit will not be asserted in self-timing mode.

#### LOL bit

In external-timing mode, the bit will be set if the PLL fails to achieve or maintain lock to the selected reference. This bit will not be asserted in self-timing mode. It is also not complementary to the SYNC bit. Both bits will not be asserted when the PLL is in the pull-in process. The pull-in process usually occur when switch to a new selected reference or recover from the LOS/LOL.

#### OOP bit

This bit indicates that the selected reference is out of the pull-in range. This is meaningful only if in external-timing mode. This bit will not be asserted in selftiming mode. The frequency offset is relative to the digitally calibrated freerun clock.

## SAP bit

This bit when set indicates that the PLL's output clocks have stopped following the selected reference because the frequency offset of the selected reference is out of pull-in range (OOP). User can write to the **Control Mode** register to program whether the PLL shall follow the selected reference outside of the specified pull-in range or just stay within the pull-in range boundary.

#### **FEE** bit

This bit indicates whether an error occurs in the frame edge detection process in slave mode or master phase align mode. For timing generator T0 only.

## **DHT** bit

This bit indicates whether the device holdover history is tracking on the current selected reference (updating by the long-term history).

#### **HHA** bit

This bit indicates the availability of the holdover history, which may be either the user provided history or the device holdover history.

## **Reference Inputs Details**

The STC5420 accepts 12 external reference inputs. The reference inputs may be selected to accept either the auto-detect acceptable reference frequency which can be automatically detected by STC5420 or manually acceptable reference frequency. Reference inputs REF11 and REF12 are LVPECL/LVDS and the remaining ten are LVCMOS. Signal polarity of REF11 and REF12 is reversible at the register **Diff Ref Polarity**. All 12 reference inputs are monitored continuously for frequency, activity and quality. Each timing generator may select any of the reference inputs when the device is in external timing mode. T4 may accept T0's output as its input via internal feedback path.

## Acceptable Frequency and Frequency Offset Detection

The STC5420 can automatically detect the frequency of the reference input when the user enable the autodetection function at the register Ref Index Selector and Ref Acceptable Freq. The acceptable autodetect frequencies are: 8kHz, 64kHz, 1.544MHz, 2.048MHz. 19.44MHz, 38.88MHz. 77.76MHz. 6.48MHz, 8.192MHz, 16.384MHz, 25MHz, 50MHz or 125MHz. These frequencies can be automatic detected continuously in the detector. Any carrier frequency change will be detected within 1ms. Each input is also monitored for frequency offset between input and the internal freerun clock. The frequency offset is a key factor to determine qualification of the reference inputs. See register Ref Index Selector and Ref Info.

STC5420 provides another option which allows the user to select the manually acceptable reference frequency for all the reference inputs, at the integer multiple of 8kHz (Nx8kHz, N is integer from 1 to 32767). Hence the manually acceptable reference frequency range is integer multiple of 8kHz from 8kHz to 262.136MHz. When a manually acceptable reference frequency is used, the user need to access the register **Ref Acceptable Freq** to set the integer N for the reference input which is selected at the register **Ref Index Selector**. Each input is monitored for frequency offset between input and the internal freerun clock. The frequency offset is shown in the register **Ref Info** when associate reference index is selected at the register **Ref Index Selector**.

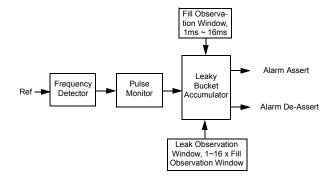

### **Activity Monitoring**

Activity monitoring is also a continuous process which is used to identify if the reference input is in normal. It is accomplished with a leaky bucket accumulation algorithm, as shown in Figure 2. The "leaky bucket" accumulator has a fill observation window that may be set from 1 to 16ms, where any hit of signal abnormality (or multiple hits) during the window increments the bucket count by one. The leak observation window is 1 to 16 times the fill observation window. The leaky bucket accumulator decrements by one for each leak observation window that passes with no signal abnormality. Both windows operate in a consecutive, non-overlapping manner. The bucket accumulator has alarm assert and alarm de-assert thresholds that can each be programmed from 1 to 64.

Figure 2: Activity Monitor

Applications can write to the following registers to configure the activity monitor: Fill Obs Window, Leak Obs Window, Bucket Size, Assert Threshold, and De Assert Threshold.

Setting the bucket size to 0 will bypass the leak bucket accumulator and assert or de-assert the activity alarm based on results of frequency detector and pulse monitor only. A non-zero bucket size must be greater than or equal to the alarm assert threshold value. The alarm assert threshold value must be greater than the alarm de-assert threshold value and less than or equal to the bucket size value. Attempted writes of invalid values will be ignored. Therefore, user must carefully plan an appropriate sequence of writes when re-configure the activity monitor. See register **Bucket Size**, **Assert Threshold** and **De Assert Threshold** for details.

Alarms appear in the **Refs Activity** register. A "1" indicates activity, and a "0" indicates an alarm, no activity. Note that if a reference is detected as a different frequency, the leaky bucket accumulator is set to the bucket size value and the reference will become inactive immediately.

### **Input Qualification**

A selected reference is "qualified" if it passes the activity evaluation and its frequency offset is within the programmed qualification range for over a preprogrammed soaking time.

A reference qualification range may be programmed up to 102.3 ppm by writing to register **Qualification Range**, and a disqualification range set up to 102.3 ppm, by writing to register **Disqualification Range**. The qualification range must be set less than the disqualification range. Additionally, qualification soaking time may be programmed from 0 to 63 seconds by writing to register **Qualification Soaking Time**. The pull-in range is the same as the disqualification range.

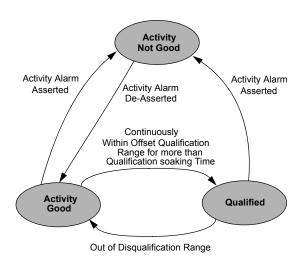

Figure 3: Reference Qualification Scheme

The frequency offset of each reference is relative to the internal freerun clock may be read by selecting the reference in the **Ref Index Selector** register and then reading the offset value from register **Ref Info**. The frequency offset of the internal freerun clock can be calibrated by writing to the register **Freerun Cali**.

Figure 3 shows the reference qualification scheme. A reference is qualified if it has no activity alarm and is

continuous within the qualification range for more than the qualification soaking time. An activity alarm or frequency offset beyond the disqualification range will disqualify the reference. It may then be re-qualified if the activity alarm is off and the reference is within the qualification range for more than the qualification time.

The reference qualification status of each reference may be read from register **Ref Qual**.

#### **Automatic Reference Election Mechanism**

The STC5420 has an auto reference elector always elect the best candidate from the reference inputs according to the revertivity status, each reference's priority and qualification. To and T4 have independent priority tables for automatic reference selection. Regardless what the current reference selection mode is (automatic, manual, or hard-wired manual), the auto reference elector always work in this mechanism. The detail description of the reference selection mode is in following sections.

The reference priority is indicated in the reference priority table which is shown in register **Ref Priority Table** individually for each timing generator. Each reference has one entry in the table, which may be set to value from 0 to 15. '0' revokes the reference from the election, while 1 to 15 set the priority, where '1' has the highest, and '15' has the lowest priority. The highest priority pre-qualified reference then is a candidate selected by the automatic reference elector. If multiple references share the same priority, the one that has been qualified for the longest time will be recommended to be the candidate. If the current highest priority reference input fails, the next-highest priority reference is selected as the candidate.

In order to avoid disturbance of the clock output, the candidate reference selected by automatic reference elector should be handled in two different mode. Revertive mode and non-revertive mode. The mode is determined by either enabling or disabling the "revertive" bit of the **Control Mode** to "1" for revertive or to "0" for non-revertive operation.

In revertive mode, the automatic reference elector will pre-empted the current candidate reference if the new recommended candidate reference has higher priority.

In non-revertive mode, the current candidate refer-

# STC5420 Synchronous Clock for SETS Data sheet

ence will not be pre-empted by any new candidate until it is disqualified.

If there is no candidate reference available, freerun or holdover will be recommended by the automatic reference elector depending on the holdover history availability.